### Modelling and Mitigation of Soft-Errors in CMOS Processors

Alireza Rohani

### Modelling and Mitigation of Soft-Errors in CMOS Processors

Alireza Rohani

#### Members of the dissertation committee:

| Prof. dr. ir. | G.J.M. Smit       | University of Twente (promoter)    |

|---------------|-------------------|------------------------------------|

| Dr. ir.       | H.G. Kerkhoff     | University of Twente (co-promoter) |

| Prof. dr. ir. | B.R.H.M Haverkort | University of Twente               |

| Prof. dr. ir. | J.C. van de Pol   | University of Twente               |

| Prof. dr. ir. | K.L.M. Bertels    | Delft University of Technology     |

| Prof. dr.     | H.S. Wunderlich   | University of Stuttgart (Germany)  |

| Dr.           | D. Alexandrescu   | iRoC Technologies (France)         |

| Prof. dr.     | P.M.G Apers       | University of Twente (chairman and |

|               |                   | secretary)                         |

|               |                   |                                    |

### **TOETS**

This work has been carried out as part of the Catrene project "TOETS" [CT302] and supported by the Netherlands Enterprise Agency.

CTIT PhD. Thesis Series No. 978-90-365-3807-7

Center of Telematic and Information Technology University of Twente, P.O. Box 217, NL-7500 AE, Enschede, The Netherlands

Copyright © 2014 by Alireza Rohani, Enschede, The Netherlands. All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage or retrieval system, without prior written permission of the author.

This thesis was printed by Gildeprint, the Netherlands.

ISBN 978-90-365-3807-7

DOI 10.3990/1.9789036538077

### MODELLING AND MITIGATION OF SOFT-ERRORS IN CMOS PROCESSORS

### DISSERTATION

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus

Prof. dr. H. Brinksma,

on account of the decision of the graduation committee

to be publicly defended

on Friday, 12<sup>th</sup> of December 2014 at 16:45

by

Alireza Rohani

born on 13<sup>th</sup> July 1983, in Damghan, Iran

### This dissertation is approved by:

Prof. dr. ir. G.J.M. Smit University of Twente (promoter)

Dr. ir. H.G. Kerkhoff University of Twente (co-promoter)

#### Abstract

The topic of this thesis is about soft-errors in digital systems. Different aspects of soft-errors have been addressed here, including an accurate model to simulate soft-errors in a gate-level net list, a simulation framework to study the impact of soft-errors in a VHDL design and an efficient architecture to minimize the effect of soft-errors in a DSP.

The first two chapters of this thesis introduce the background knowledge with regard to soft-errors. Chapter three introduces a simulation framework to study the impact of soft-errors in complex digital systems modelled in the VHDL language. This framework has been introduced to resolve the enormous CPU time typically required in simulation-based soft-error experiments.

Chapter four introduces two realistic models that can simulate the impact of soft-errors in a 45-nm CMOS technology node at gate level. One of the approaches has been extracted from radiation testing along with using a transistor-level soft-error analysis tool. Another approach has been developed by analysing the behaviour of soft-errors in a 45-nm CMOS technology node.

In chapter 5, some unique features of DSPs have been exploited to introduce low-overhead soft-error mitigation architectures to minimize the impact of soft-errors in a DSP processor. This mitigation technique concerns irregular parts of a processor (such as the control unit and data path). The unique features of DSP processors are the existence of several functional units, a limited number of different opcodes in each functional unit and also a highly-repetitive instruction flow in a DSP workload. Moreover, the mitigation method which has been developed for a single core has been applied to a multi-core environment in chapter 6 to propose a soft-error mitigation technique for multi-core architectures.

As a conclusion, based on simulated data and experiments, this thesis proposes a methodology to investigate the impact of soft-errors during the design phase of a digital system.

This page intentionally left blank.

### **Nederlandse samenvatting**

Het onderwerp van dit proefschrift betreft sporadische fouten in digitale systemen. Deze sporadische fouten worden veelal aangeduid als *soft errors*. Verschillende aspecten van soft errors worden belicht in dit proefschrijft, waaronder een accuraat simulatiemodel om soft errors op poort-niveau te emuleren, een simulatieraamwerk om de gevolgen van soft errors in een VHDL-ontwerp te bestuderen en een efficiënte architectuur om de effecten van soft errors in DSP's te minimaliseren.

De eerste twee hoofdstukken van dit proefschrift behandelen de achtergrondkennis met betrekking tot soft errors. Hoofdstuk drie introduceert een simulatieraamwerk om de gevolgen van soft errors in complexe, in VHDL beschreven digitale systemen te onderzoeken. Het raamwerk wordt geïntroduceerd om extreem lange rekentijden, die normaliter gepaard gaan met simulatiegebaseerde soft error-experimenten, te voorkomen.

Hoofdstuk vier introduceert twee realistische modellen die de effecten van soft errors op poort-niveau emuleren in 45-nm CMOS-technologie. De eerste methode is gebaseerd op stralingsmetingen tezamen met een soft error analyse-applicatie op transistorniveau. De tweede methode is ontwikkeld op basis van de analyse van de fysieke gevolgen van soft errors in 45-nm CMOS-technologie.

In hoofdstuk 5 wordt een architectuur met lage complexiteit geïntroduceerd waarmee de effecten van soft errors in DSP's teniet worden gedaan door gebruik te maken van enkele speciale eigenschappen van DSP's. Deze methode werkt op de onregelmatige onderdelen van de processor (zoals de regeleenheid en het datapad). De speciale eigenschappen van DSP's betreffen 1) het bestaan van verschillende functie-eenheden, 2) een beperkt aantal opcodes in elke functie-eenheid en 3) programma's met veel herhaaldelijk uitgevoerde instructies. Daarnaast kan de methode, hoewel deze ontwikkeld is om soft errors in single-core systemen te verhelpen, ook toegepast worden in een multicore context, zoals beschreven in hoofdstuk 6.

Tot slot, is er een methode ontwikkeld op basis van simulatieresultaten en experimenten om al tijdens de ontwerpfase rekening te houden met soft errors en de gevolgen daarvan te minimaliseren.

This page intentionally left blank.

### **Acknowledgements**

Looking back to my life reminds me of many great people who have influenced me to become a better human being. To mention a few, I would like to thank Mr. Abolfazl Khalilnejad, my first English teacher back in high school who was not only one of the greatest teachers I have ever had, but also a symbol of responsibility and discipline to me. I would also like to give my appreciation to Dr. Hamid Reza Zarandi, my supervisor during my master degrees at Amirkabir University of Technology.

Starting my PhD in the Netherlands back in 2010 went smoother with having wonderful people around me. To name few, I would like to thank Masi Amirpour, Pouria Zand, Marziyeh Malekinajad, Siavash Aflaki, Mitra Baratchi, Sina Behfard, Alireza Masum, Zahra Taghikhani, Amirhossein Ghamarian, Wim Korevaar and Majid Bahrepour.

I would like to appreciate my promoter, Prof. Gerard Smit, for giving me the opportunity to carry out my PhD in CAES group. I would like to give my greatest appreciation to my daily supervisor, Dr. Hans Kerkhoff. He has not only helped me regarding my PhD research, but I learned responsibility, dedication and morality from him. I could not think of any better supervisor than Hans.

I would like to thank people of the CAES group, especially Muhammad Aamir Khan, Ahmed Ibrahim, Hassan Ebrahimi, Andreina Zambrano, Jinbo Wan, Yong Zhao, Wim Korevaar, Robert de Groote, Koen Blom, Marco Gerards, Philip Hölzenspies and Bert Molenkamp. I especially would like to thank Marlous Weghorst, Thelma Nordholt – Prenger, Nicole Baveld, and Bert Helthuis that made the CAES group a more pleasant environment to work.

I would also like to thank my paranymphs, Anja Kolesnichenko and Amir Meshkat for helping me during my defence. I am thankful of Wim Korevaar how helped me to translate the summary of this thesis to Dutch.

I would like to thank my parents, Masoume Amirahmadi and Nematollah Rohani who taught me self-devotion. I believe being raised by those made me a person who is eager of pursuing his dreams. Also, thanks to my two lovely and amazing sisters, Aida and Mitra. There were many moments in my life when I missed them here in the Netherlands.

And special thanks to my lovely and beautiful wife, Mahroo Zandrahimi. I met Mahroo during my studies in 2009 and she made my academic life special as

well. She always understood my work situation, especially during this last year when I was travelling between Enschede and Delft. She means an endless source of kindness, love and support to me. I also like to thank my father-in-law, Dr. Morteza Zandrahimi for his support.

Alireza Rohani, November 2014

### **Contents**

| 1 Introduction                                                            | 1  |

|---------------------------------------------------------------------------|----|

| 1.1 Introduction                                                          | 2  |

| 1.2 Motivation and problem statement                                      | 7  |

| 1.3 Outline of the thesis                                                 | 8  |

| 2 Sources, Terminology and Evaluation Methods of Soft-Errors              | 11 |

| 2.1 Introduction                                                          | 12 |

| 2.2 Terminology                                                           | 14 |

| 2.3 The sources of soft-errors                                            | 20 |

| 2.3.1 Neutrons                                                            | 20 |

| 2.3.2 Alpha radiation                                                     | 21 |

| 2.4 Soft-error vulnerability analysis                                     | 22 |

| 2.4.1 Hardware-based fault-injection techniques                           | 24 |

| 2.4.2 Software-based fault-injection techniques                           | 26 |

| 2.4.3 Simulation-based fault-injection techniques                         | 27 |

| 2.4.4 Emulation-based fault-injection techniques                          | 29 |

| 2.5 Architecture of our target processor                                  | 31 |

| 2.6 Conclusions                                                           | 33 |

| 3 A Framework for Accelerating Soft-Error Analysis in HDL Designs         | 37 |

| 3.1 Introduction                                                          | 38 |

| 3.2 Simulation-based fault analysis                                       | 40 |

| 3.2.1 State-of-the-art simulation-based fault-injection                   | 41 |

| 3.2.1.1 Built-in commands                                                 | 41 |

| 3.2.1.2 Code-modification techniques                                      | 43 |

| 3.2.2 Accelerated simulation-based fault-injection framework              | 45 |

| 3.3 The developed fault-injection framework                               | 47 |

| 3.3.1 Fault-injection units                                               | 47 |

| 3.3.2 Embedding FIUs in the fault-injection phase                         | 51 |

| 3.4 Time acceleration results                                             | 57 |

| 3.5 Level of hierarchy versus results of simulation-based fault-injection |    |

| 3.6 Conclusions                                                           | 71 |

| 4 Pulse-Length Determination Techniques for Rectangular SET Faults        | 75 |

| 4.1 Introduction                                                          | 76 |

| 4.2 Conventional determination of pulse length in                         |    |

| rectangular SETs                                                          | 79 |

| 4.3 The circuit-based determination approach                              | 81 |

| 4.4 The analytical-based determination approach                           | 88 |

| 4.5 Details of fault-injection                                            | 93 |

| 4.6 Experimental results                                         | 95  |  |

|------------------------------------------------------------------|-----|--|

| 4.7 Conclusions                                                  | 101 |  |

| 5 Soft-Error Mitigation Techniques for DSP Functional units      | 105 |  |

| 5.1 Introduction                                                 |     |  |

| 5.1.1 State-of-the-art                                           | 107 |  |

| 5.1.2 Our DSP mitigation techniques                              | 109 |  |

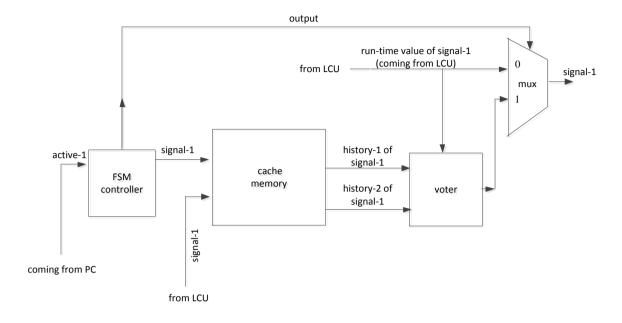

| 5.2 Our SET masking mechanism in LCUs                            | 112 |  |

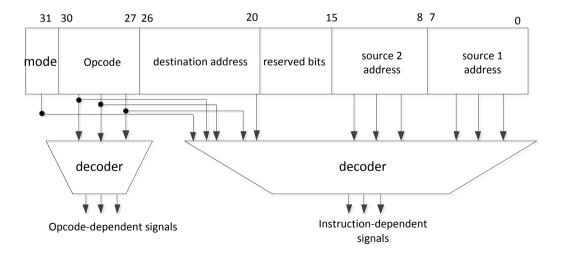

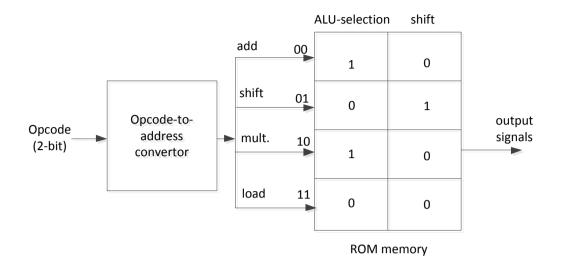

| 5.2.1 Opcode-dependent control signals                           | 113 |  |

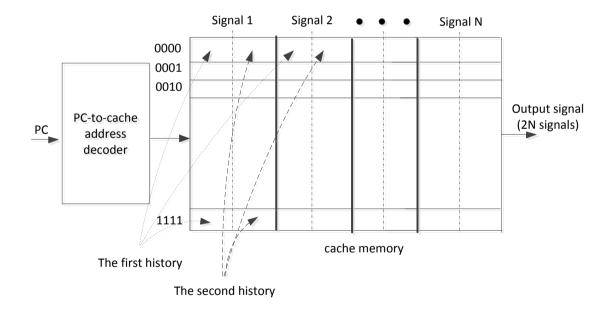

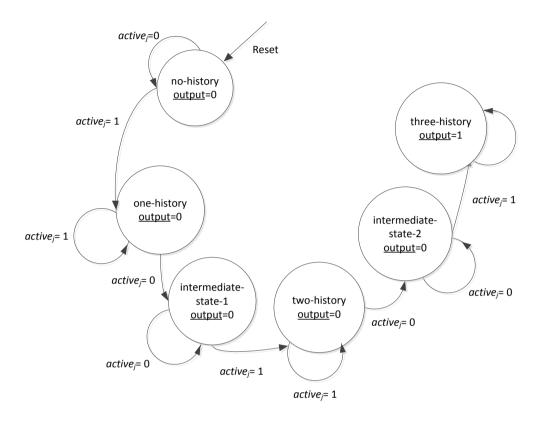

| 5.2.2 Instruction-dependent control signals                      | 115 |  |

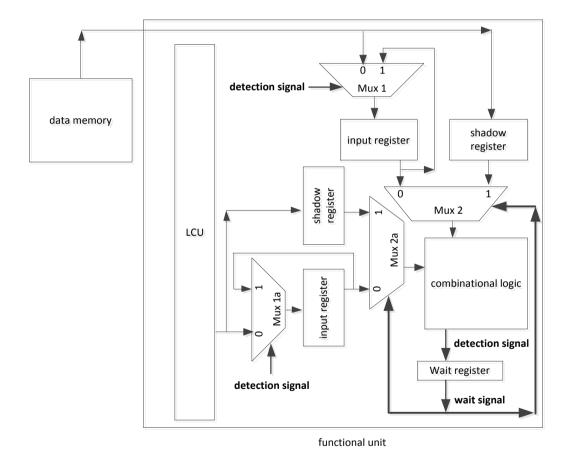

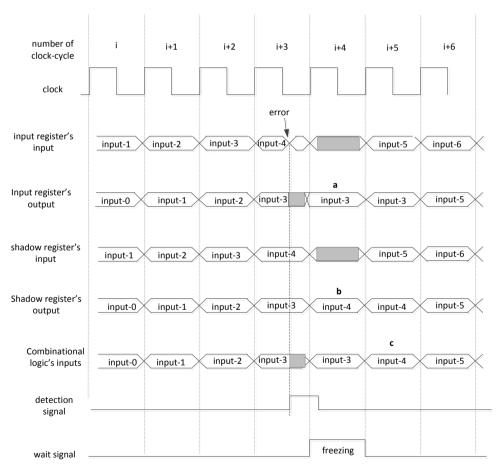

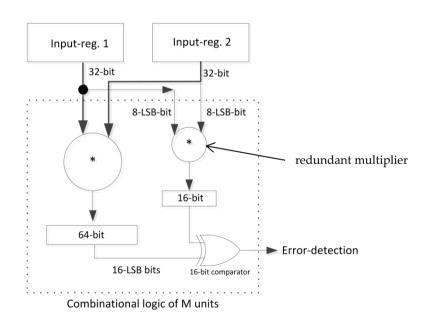

| 5.3 A recovery mechanism in combinational logic                  | 121 |  |

| 5.4 Experimental results                                         | 125 |  |

| 5.4.1 Area overhead and performance degradation                  | 125 |  |

| 5.4.2 SET sensitivity                                            | 128 |  |

| 5.4.3 Comparison of our methods with other methods               | 129 |  |

| 5.5 Conclusions                                                  | 130 |  |

| 6 Using Multi-core Architectures to Mitigate Soft-Errors         | 133 |  |

| 6.1 Introduction                                                 | 134 |  |

| 6.2. State-of-the-art methods                                    | 136 |  |

| 6.3. The motivation to propose our technique                     | 141 |  |

| 6.4 Our approach for soft-error mitigation in multi-core         |     |  |

| systems                                                          | 142 |  |

| 6.4.1. Soft-error detection approach                             | 143 |  |

| 6.4.2 Soft-error recovery approach                               | 146 |  |

| 6.4.3 Operational phases of our architecture                     | 149 |  |

| 6.5 Additional features of our architecture                      | 151 |  |

| 6.6 Experimental setup and evaluation of our approach            | 154 |  |

| 6.6.1 Experimental set-up                                        | 154 |  |

| 6.6.2. The soft-error coverage                                   | 155 |  |

| 6.7 Conclusions                                                  | 158 |  |

| 7 Conclusions, Contributions and Recommendations for Future Work | 161 |  |

| 7.1 Introduction                                                 | 162 |  |

| 7.2 Contributions                                                | 162 |  |

| 7.3 Conclusions                                                  | 164 |  |

| 7.4 Future work                                                  | 165 |  |

| List of our publications                                         | 168 |  |

| Biography                                                        | 169 |  |

### **List of Acronyms**

**AC** Accumulator

ADIRUs Air Data Inertial Reference Units

**ALU** Arithmetic Logic Unit

**ATPG** Automatic Test Pattern Generation

**CMOS** Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

CR Checkpoint and Recovery

DAC Duplication And Comparison

**DMR** Modular Redundancy

**DRAM** Dynamic Random Access Memory

**DSP** Digital Signal Processing

DUE Detected-Unrecoverable-Error

DWC Duplication With Comparison

EDA Electronic Design Automation

**EDAC** Error Detection and Correction Codes

**EMI** Electro Migration Interference

FIR European Space agency

FIR Finite Impulse Response

FIS Fault Injector Signal

FIT Failure In Time

Fills Fault Injection Units

**FPGA** Field Programmable Gate Arrays

**GLN** Gate Level Net-list

HBFI Hardware-Based Fault InjectionHDL Hardware Description Language

ICs Integrated Circuits

LCU Local Control Unit

LSB Least Significant Bits

**LUT** Look-Up Table

MEU Multiple Memory Upset

MeV Mega electron Volt

MOS Metal Oxide Semiconductor

NASA Aeronautics and Space Administration

NoC Network on Chip

PC Program Counter

QoS Quality of Service

RIIF Reliability Information Interchange Format

**RISC** Reduced Instruction Set Computer

**RMT** Redundant Multi-Threading

ROM Read only Memory

RTL Register Transfer Level

SDC Silent Data Corruption

SDF Standard Delay Format

SEE Single Event Effect

SEM Soft Error Mitigation

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SoC System on Chip

SPARC Scalable Processor Architecture

SRAM Static Random Access Memory

STEM Soft and Timing Error Mitigation

TMR Triple Modular Redundancy

VLIW Very long Instruction Word

VLSI Very Large Scale Integration

VPI Verilog Programming Interface

## CHAPTER 1

Introduction

### 1.1 Introduction

The unprecedented progress of CMOS technology has enabled digital systems to be emerged ubiquitously in every aspect of our life. Nowadays it is difficult to imagine a task in which digital computing is not involved. This includes portable electronic systems like laptop computers, cellular phones, and music players up to different embedded computing systems in the medical, automotive and avionics industry. The sharp rate of growth in CMOS technology has been sustained by shrinking the minimum technology sizes of transistors to smaller and smaller dimensions along with the continuous reduction in the operating and threshold voltages [Hir02]. While this technology scaling has provided modern VLSI systems with a higher performance and lower power consumption, their sensitivity to certain types of faults has dramatically increased. As a result, the reliability of a system which are implemented in a modern CMOS process node is a key concern [Cao09].

The required level of reliability of a device depends on different parameters. For example, a very brief momentary malfunction in an audio device embedded in a car might cause no harm other than inconvenience and a slight reduction of Quality of Service (QoS). However, even a slight temporary malfunction in the lane-detection system of a modern car might lead to the loss of human life.

As a real example, the sudden dive of a Qantas flight, back in 2008 [Wik08] will be briefly discussed. The airplane had to carry out an emergency landing due to an inflight accident featuring a pair of sudden uncommanded pitch-down manoeuvres that resulted in serious injuries to many of the passengers. The final report issued in 2011 concluded that the accident occurred due to a failure mode affecting one of the aircraft's three air-data inertial reference units (ADIRUs). The failure mode was further tracked down to design limitations, in which in a very rare and specific situation, multiple spikes were formed in one of the ADIRUs which in turn could command the aircraft to pitch down.

A primary source of momentary malfunction of advanced CMOS computing is known as soft-errors [Nic11]. A soft-error, also referred to as

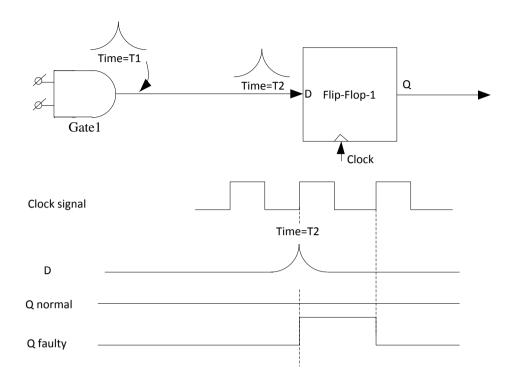

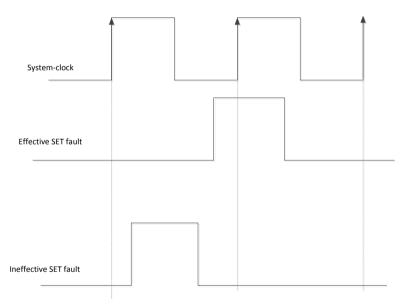

Single Event Effect (SEE), can occur when an energetic particle from extraterrestrial space or from impurities in packaging material hits the surface of a CMOS transistor. As a consequence of this collision, a current glitch might be generated in the transistor channel, which subsequently results into a voltage glitch at a circuit node. This voltage glitch has the potential to propagate into the subsequent logic gates of the system and can even cause a functional failure of the system. Soft-errors can occur in any internal node of a circuit, at random times. Depending on the timing of the clock, glitches can propagate to higher hierarchical levels and load a wrong value into a latch or flip-flop. For example, in Figure 1.1, a glitch has been generated in logic gate1 at time T1. This glitch has reached the positive edge-triggered flipflop-1 at time T2. Because the positive clock-edge for flip-flop-1 is occurring at time T2, an erroneous value which is now 1 instead of 0, will be stored in the flip-flop. However, this erroneous value will not reside permanently in the flip-flop; so when a new value reaches the positive edge-triggered flipflop in the next clock-cycle, the flip-flop stores the new value. Hence, the output of the flip-flop will be high for one clock-cycle.

Figure 1.1. Loading an erroneous value in a flip-flop due to a glitch in a circuit.

Historically speaking, the first concern of soft-errors emerged during the nineties when several studies repeatedly showed that the majority of system failures in modern digital circuits can be categorized as soft-errors, rather than traditional manufacturing errors or permanent faults [Gre94]. Recent VLSI technology trends such as shrinking the transistor features has helped the design of transistors for higher integration density, higher performance and lower power consumption. Higher integration densities, increase in operating frequencies along with reduction of operating supply voltage all have considerably increased the soft-error vulnerability of current digital systems [Cao09]. Moreover, the increased use of wireless technology, such as Wi-Fi and mobile phone transceivers has increased the hostility of our environment as a threat from soft-errors.

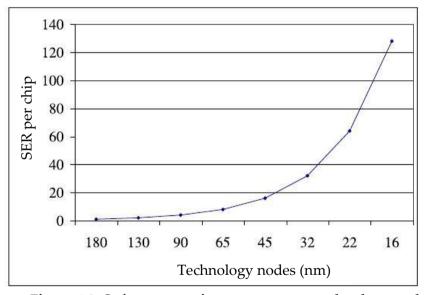

The amount of erroneous glitches in a transistor depends on many parameters, being the speed of the circuit, the environment where the system is being used, altitude, etc. While the soft-error rate of individual transistors are projected to increase with every new generation of VLSI, incorporating more and more transistors into a device even exacerbates the problem. Taking into account all the above-mentioned consequences of technology scaling, it has been consistently proven that softerrors are a major threat of circuit/system reliability for the sub-100nm technology [Kar04]. Figure 1.2 shows the rate of soft-errors for a matured technology as well as the projected soft-error rate for the 16nm process node. As can be seen in this Figure, for a technology node larger than 100nm, the soft-error rate was not a concern at all. However, if the technology shrinks to 45nm, a typical Intel processor chip can experience 20 failures in its life time. This number will increase exponentially with shrinking dimensions in technology.

Figure 1.2. Soft-error rate in recent process technology nodes [Kar01].

Historically, soft-errors have been mainly of concern to those systems designed to be used in safety-critical systems, or systems that were going to be used in hostile environments, such as satellites, spaceships and aircrafts. Those particular applications could benefit from expensive fabrication technology and complex fault-tolerant solutions to reduce the impact of soft-errors. However, those expensive advances in developing fault-tolerant designs will not be cost-effective for mass-produced consumer products. Furthermore, emerging issues like process variations have introduced additional sources of soft-errors [Xfu09] which exacerbate the sensitivity of present computer systems to soft-errors.

As a conclusion, the concerns of soft-errors for current embedded systems are not limited to space applications anymore, since device scaling accompanied by supply power reduction has caused reliability issues for embedded system manufactured in sub 100nm process nodes.

### 1.2 Motivation and problem statement

In the TOETS (Towards One European Test Solution) project, developing new methods to deal with failures occur in sub 100nm technology nodes are investigated. Our special concern in this thesis is to develop a soft-error hardened system to be used in automotive industry. At the time of writing of this thesis (2014), full-hybrid and X-by-wire cars are already driving in the streets (such as Tesla [Tes14] and Nissan [Nis14]). Moreover, the first auto-drive car has been authorized to be emerged on the streets of the USA (Google project) [Goo14].

So, it is no longer possible to consider the automotive industry as a low-critical domain regarding soft-errors. For example, Toyota had one of the biggest recalls of the automotive industry across the globe in 2010 to fix the electronic systems of its cars. The problem was claimed to be related to the very sensitive parts of the car with regard to soft-errors [Men12, Fin13a, Fin13b]. It was shown that a glitch in the electronic system of the car could influence the functionality of its acceleration system.

The other important concern regarding the automotive industry is the total cost, which limits the usage of expensive soft-error mitigation solutions. As a result, the digital architect has to develop an electronic device that has an acceptable vulnerability level concerning soft-errors, while its final cost/performance is acceptable to be used in a car.

Since safety-critical applications in a car are more towards DSP applications, such as lane detection or distance prediction, our main goal in this work is to develop a soft-error hardened architecture for DSP processors which satisfies the performance criteria.

This thesis addresses the soft-error problems occurring in DSP processors fabricated in a 45nm technology node. Several aspects of soft-errors, from an architectural soft-error model to proposing light-weight architectural solutions for detection and correction of soft-errors in single and multicore DSP systems will be studied throughout this thesis. Specifically, the problem statement can be stated as follows:

- A soft-error analysis framework to assess the effect of softerrors in complex processors needs to be investigated. Traditional simulation-based fault-injection frameworks are slow and not practical to conduct soft-error analysis on complex DSP processors. So, accelerated frameworks are essential for soft-error analysis on complex digital processors.

- An efficient model to emulate the impact of soft-errors in sub 100nm technology nodes needs to be developed. As the CMOS technology of implementation shrinks beyond 45nm technology nodes, already developed fault models are not practical anymore. A realistic and accurate simulation model of soft-errors in a 45nm and beyond technology nodes is essential in order to study the impact of soft-errors in complex digital processors.

- While there are many general soft-error mitigation mechanisms in digital processors, we are especially interested to use the unique characteristics of DSP processors, such as existence of identical resources, to develop an efficient faulttolerant mechanism. Moreover, we want to investigate unstructured parts of a processor, such as the data-path or control-logic, since these two units cannot be protected by conventional fault-tolerance methods.

- Since the increasing usage of multicore architectures in modern digital systems, we also want to develop a faulttolerant architecture customized for multicore architectures consisting of DSP cores. Moreover, the existence of several identical cores in multicore architecture might be very useful for soft-error mitigation mechanisms.

### 1.3 Outline of the thesis

The remainder of this thesis has been organized as follows:

Chapter 2 describes the basic terminology of soft-errors, including the origin of soft-errors and a survey of the state-of-the-art methods dealing with detection and correction of soft-errors in processors. The details of our simulation-based fault-injection framework will be discussed in chapter 3. This framework is able to inject conventional logic gate-level fault models, like a fixed-duration glitch, into a Hardware-Description-Language (HDL)-based design. In chapter 4, a realistic simulation model for soft-errors in 45nm process nodes will be proposed. Two unique techniques to detect and correct soft-errors in DSP processors are described in chapter 5. The framework provided in chapter 3 along with the realistic fault model described in chapter 4 form the basis of two advanced methods being developed to harden a DSP processor with respect to soft-errors. In chapter 6, the architecture of a multi-core design will be used to develop a detection and correction method. Since chapter 6 combines the fault-tolerant architecture of a single core from chapter 5, this chapter must be read before reading chapter 6. Finally, in chapter 7, conclusions are given and some suggestions for future work are provided.

### References

- [Cao09] Y. Cao, P. Bose, J. Tschanz, "Reliability challenges in Nano-CMOS design," IEEE Design and Test of Computers, pp. 6-7, 2009.

- [Fin13a] Financial Times Press, www.sddt.com, 2013.

- [Fin13b] Financial Times Press, www.eetimes.com, 2013.

- [Goo14] Google Self-Driving Car Project, www.GoogleSelfDrivingCars.com, 2014.

- [Gre94] L. Gregory, S. Gwan, K. Ravishankar, "Device-level transient fault modeling," in International Symposium on Fault-Tolerant Computing, pp. 86-94, 1994.

- [Hir02] M. Hirose, "Challenge for future semiconductor development," in Microprocessors and Nanotechnology Conference, pp. 2-3, 2002.

- [Kar01] T. Karnik, B. Bloechel, K. Soumyanath, "Scaling trends of cosmic ray induced soft-errors in static latches beyond 180nm," in International Symposium on VLSI Circuits, pp. 61-62, 2001.

- [Kar04] T. Karnik, P. Hazucha, J. Patel, "Characterization of soft-errors caused by Single-Event-Upset in CMOS processes," in IEEE Transactions on Dependable and Secure Computing, Vol. 1, No. 2, pp. 128-143, 2004.

- [Men12] Report by MentorGraphics, www.chipdesignmag.com, 2012.

- [Nic11] M. Nicolaidis, "Soft-errors in Modern Electronic Systems," in Frontiers in Electronic Testing, ISBN 978-1-4419-6993-4, 2011.

- [Nis14] www.nissanusa.com/electric-cars/leaf, 2014.

- [Tes14] www.teslamotors.com, 2014.

- [Xfu09] X. Fu, T. Li, J. A. B. Fortes, "Soft-error vulnerability aware process variation mitigation," in International Symposium on High Performance Computer Architecture, pp. 93-104, 2009.

- [Wik08] WikiPedia, http://en.wikipedia.org/wiki/Qantas\_Flight\_72, 2008.

# CHAPTER 2

Sources, Terminology and Evaluation Methods of Soft-Errors

ABSTRACT- This chapter will cover the terminology of soft-errors, discuss the sources of soft-errors and also different evaluation methods to assess the vulnerability of a system with regard to soft-errors will be explained. Moreover, the details of our case study the Xentium processor, will be presented at the end of this chapter. It will serve later on as a test bench in developing a fault-injection framework, a new model for soft-errors and also its architecture will be modified to develop a reliable and low overhead DSP architecture to mitigate soft-errors.

### 2.1 Introduction

Until a decade ago, there was no consistency on whether it would make sense to invest in the mitigation of soft-errors in digital circuits or not. In general, a soft-error does not concern ordinary and low-critical applications. For example the cell-phone or audio industry is not concerned about soft-errors at all. However, if a correct and timely operation of a system is critical, especially in harsh environments, soft-errors will be an issue for sure. Some examples of critical systems are: the break system in modern electrical cars (drive-by-wire cars), electronic systems of an airplane or the communication backbone of a satellite. In these systems, the correct functionality of the system can be lost, temporarily or permanently, by the effect of soft-errors. If the impact of soft-errors is momentary, then a short malfunction will appear in the device. If the error manifests in the system, it might be required to reset the system completely, which can be sometimes very costly in terms of performance loss. This because the entire workload needs to be executed again.

Since the nature of these temporary malfunctions are quite random, it is very hard to trace a failure which has been caused by a soft-error. These soft-error induced failures are even more harder to tackle when new information has already been loaded into the logic that has been affected by soft-errors.

Another concern which makes tackling soft-error induced failures very hard, is the limitation of traditional test methods, such as Automatic Test Pattern Generation (ATPG). Because soft-errors appear and disappear in a very brief period of time, a permanent isolation of an affected net or logic gate is not practical in dealing with soft-errors.

As a result, all the methods that deal with soft-errors should be built based on an <u>online</u> detection and correction mechanism to mask the effect of soft-errors as soon as possible. On the other hand, a failure which has been induced by a soft-error is not reproducible, since it is random in nature; hence the online soft-error mechanism should be able to stop the propagation of a soft-error as soon as possible. One of the solutions which can be used to prove that a soft-error has caused a failure in a system, is to log every status of a system and then trace the root of the problem. However, it is generally too costly to log the status of all the components of a design at every instance of time.

After the emerging of soft-error induced failures in modern digital systems during the nineties, different industrial sectors started research programs to address the problem of soft-errors. To name a few: Intel, IBM and Fujitsu in the semiconductor sector, Boeing, Airbus, Ericsson-Saab Avionics in the avionics sector, and the European Space Agency (ESA) and National Aeronautics and Space Administration (NASA) in space applications. As a real case of a soft-error induced failure, some random failures were found in a computer on a commercial aircraft in 1993 [Ols93, Yuh11]. The circuit which was affected by the random malfunctioning was a 256 kilo-bit SRAM which showed failures at a rate of one error per eighty days. Moreover, there were some reports by IBM and Boeing in which a strong correlation between the rate of random malfunctioning and the altitude above sea level of the aircraft electronic system was recorded [Tab93]. Apart from these two well-known examples of soft-errors in digital systems, some other examples induced by soft-errors in the semiconductor industry have highlighted the importance of soft-error measurements in the electronic design industry. Some examples have been shortly listed in the next paragraph based on examples from [Yuh11].

A phenomenon which is known as the Hera problem has been reported by IBM [Zie96]. During those years, IBM observed an increase in the rates of failures in Large Scale ICs (LSI) memories manufactured in the USA. Surprisingly, identical memories which were produced in Europe did not have this problem. The problem was traced back to the radiation which was emitted from the packaging material of a ceramic package. The problem

was further traced back to impurities inside the ceramic packaging which emit radioactive rays and caused the memory cells to toggle their values randomly in time.

The second example is a problem being observed in a data server line, the Enterprise of Sun [For00]. The server occasionally crashed for a brief amount of time. The rate of failures was as high as four times in one month and they were induced by high sensitivity of memory cells with regard to soft-errors.

Another example concerned Cisco systems [Cis03]; some routers showed random failures caused by radiation-induced soft-errors. After Error Detection and Correction Codes (EDAC) [Nic11] were implemented in the memories, the rate of soft-errors diminished.

The rest of this chapter serves as an introduction to soft-errors. First, the terminology of soft-errors will be discussed. Then, the origin of soft-errors will be covered. Different methods to evaluate the vulnerability of systems against soft-errors will be discussed. Finally, the details of our case study, which is the Xentium processor [Rec11] will be provided. This processor will be used to analyse the impact of soft-errors in a complex digital system and also for the development of efficient methods to mitigate soft-errors.

### 2.2 Terminology

This section provides the common terminology which is being used by the soft-error community [Nic11, Sha11].

The main cause of soft-errors in integrated circuits are high-energy particles coming from extra-terrestrial sources or from inside chip packaging materials. In case an energetic particle hits a CMOS transistor, it has the potential to produce a localized ionization which is able to change the data which has been latched in a flip-flop or a latch. If a particle has sufficient energy to change the charge content of a memory from 0 to 1, or vice versa, this phenomenon is called Single Event Upset, known as SEU [Bau02, Sha11]. However, this change in the content of the memory is not a permanent one, such as errors caused by stuck-at-0 or stuck-at-1 faults

[Cro99]. So if the affected latch or flip-flop is loaded with new data, the impact of the SEU will be masked. However, in many situations the erroneous value has the potential to propagate into the system before overwriting of data occurs. In this case, the SEU has the potential to modify the entire functionality of a system. These kind of errors are called <u>soft</u> since the actual hardware of the circuits is not permanently damaged. Hence, if the system is reset or is reloaded with the proper state, the system can operate correctly again.

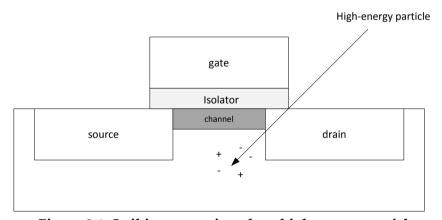

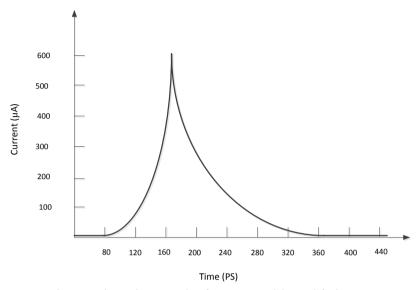

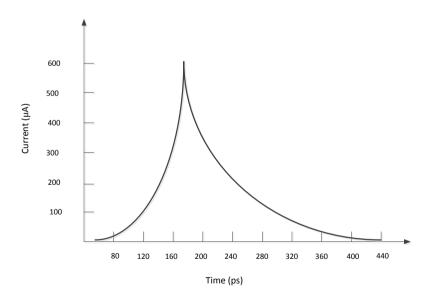

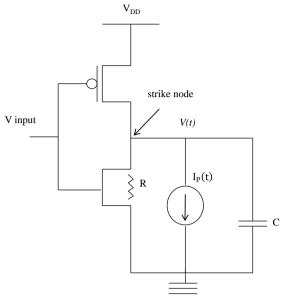

Figure 2.1 shows the moment when a high-energy particle hits a CMOS transistor. If the high-energy particle has sufficient energy, which is more than 1 Mega-electron-Volt (MeV), it has the potential to deposit a dense track of electron-hole pairs as they pass through a p-n junction [Shi02]. Some of the deposited charge will be absorbed by the gate of the transistor and form a short duration pulse of current at the internal circuit node. This short current pulse is depicted in Figure 2.2. This figure shows that a current pulse with maximum amplitude of  $600\mu A$  has been produced by the particle. The duration and amplitude of this momentary pulse depends on the technology of implementation of the transistor, which can be 45nm, 22nm, etc., the type and energy of high-energy particle as well as the temperature.

Figure 2.1. Striking a transistor by a high-energy particle.

Figure 2.2. The produced perturbation caused by a high-energy particle.

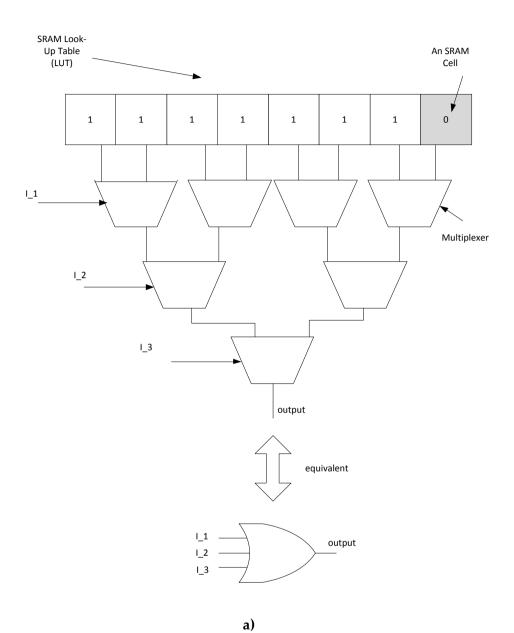

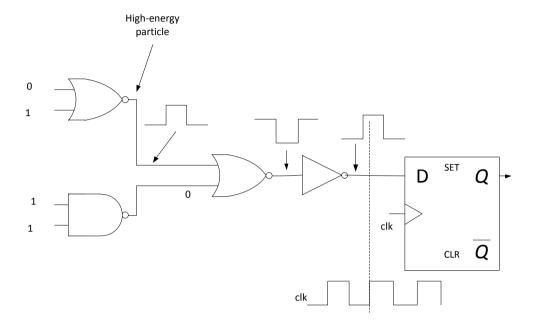

Figure 2.3a shows a sequence of SRAM cells which have been configured as a Look-Up Table (LUT) in order to implement a logic OR function. Suppose that a radiation particle has hit the last SRAM cell (Figure 2.3b) and changed the stored value from 0 to 1. In this situation, the logic which will be implemented by the new configuration is a permanent stuckat-1 value connected to Vdd; this has been shown in the equivalent logic gate in Figure 2.3b. It will be shown later on that error detection and correction codes are a powerful mechanism to mitigate this kind of errors.

Figure 2.3. A soft-error in a Look-Up Table. a). the correct operation of the Look-Up Table. b). the erroneous operation of the Look-Up Table.

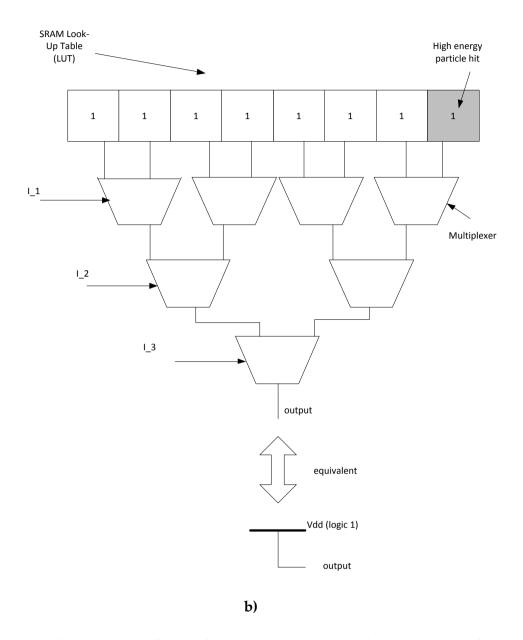

Another phenomenon caused by soft-errors is the Single Event Transient (SET) which occurs if a momentary pulse (glitch) is generated at the output of a logic gate. This glitch has the potential to traverse through other combinational logic gates and reach a flip-flop or logic gate input in the succeeding hierarchy. If the clock-edge occurs at the same time when the glitch reaches a flip-flop input, the erroneous value will be latched into the flip-flop and the status of the circuit will be changed.

Figure 2.4 shows the propagation of a SET in several logic gates and reaching a memory cell. As can be seen in this figure, in the normal situation the value of 0 should be stored in the flip-flop, but as a result of a particle hit, the erroneous value of 1 has been latched in the flip-flop. This phenomenon is different from the SEU, since the value of the flip-flop has not been changed directly, but a <u>wrong</u> value has been produced by the combinational logic and then captured by the flip-flop. This type of error is very difficult to handle.

Figure 2.4. Propagation of a SET in the combinatorial part of a circuit.

A metric which is used to refer to soft-errors is the frequency of occurrence of errors. This metric is commonly referred to as the soft-error rate or SER. The SER depends on many factors including altitude above sea level and temperature.

In the following section, the origin of soft-errors and their occurrence rate will be discussed.

### 2.3 The sources of soft-errors

There are multiple physical phenomena that induce soft-errors in a MOS digital circuit, the two dominant ones being neutron and alpha particles. The effect of these two sources are quite different from each other and they will be discussed in different subsections.

#### 2.3.1 Neutrons

High-energy neutrons are one of the most dominant sources of softerrors [Wan07]. Close to the orbit of planet Earth, the prime source of neutrons is cosmic radiation. The cosmic rays are radiation fluxes which consist of high-energy particles originating from outer space. There are two main types of cosmic radiation that induce soft-errors: solar cosmic rays and galactic cosmic rays [Anc03].

Solar cosmic rays originate from the sun and are primarily composed of proton and helium particles. Protons dominate the solar cosmic ray flux and are typically low energy particles. Galactic cosmic rays are high-energy particles that penetrate into the orbit of planet Earth from the outside of our solar system. In general, galactic cosmic rays typically have a very large energy and are the cause of most of the soft-errors in satellite and aerospace avionics.

When the galactic cosmic radiation reaches ground sea level, the flux of particles is primarily composed of muon, proton, neutron, and pion particles [Zie81]. Neutrons are the most likely particles to cause a soft-error in a circuit since they have the highest energy.

As a result of the interaction with the atmosphere, the radiation flux depends on the altitude. For example, there is about a 10 times difference in flux between the sea level and an altitude of 10000 feet [Zie81]. Thus, computers operating at a high altitude, for example in aircrafts, can experience soft-error rates in excess of an order of magnitude than they would have at sea level [Wan07].

The influence of neutron particles can be reduced to negligible levels with very strong physical shielding. For example, each 33 centimetres of concrete can reduce the neutron flux by approximately 1.4 times [Dir03]. As a consequence, shielding is an impractical soft-error mitigation solution in many computing installations where reliability is demanding, such as in embedded systems.

### 2.3.2 Alpha radiation

Another dominant source of soft-errors is considered to be alpha particle radiation [Wan07]. An alpha particle is composed of two protons and two neutrons. Alpha particles have a very high-energy as well as a large mass, and can be easily shielded by simple materials. Even a piece of paper

is sufficient to shield alpha-particle radiation. Moreover, alpha particles can travel only a few centimetres in the air. Consequently, alpha particles should originate from a source very close to the circuit to be able to cause a soft-error.

The discovery of alpha particles to produce soft-errors goes back to the nineties when the Intel corporation experienced some random behavior in its 16-Kbyte DRAM memories caused by packaging [Bau05]. Intel then tracked the origins of suspected radioactive impurities, and they found that a new LSI ceramic package was used for these chips. The package used uranium materials and consequently the level of radiation emitted to the chips was higher than normal.

Nowadays, even very low alpha-particle rates can cause a malfunction in 45nm CMOS circuits and below. Packaging materials should therefore be selected carefully to reduce the amount of emission regarding alpha particles. Moreover, it turned out to be possible to shield the emission of alpha particles with shielding materials during packaging even if the technology was still less sensitive to alpha particles [Adv05].

Regarding the contribution of these particles to cause a soft-error, the neutron soft-error rate is the dominant one. However, shrinking technology dimensions along with reducing supply voltages has made the alpha particle the second dominant source of soft-errors [Adv05].

# 2.4 Soft-error vulnerability analysis

Despite the fact that detection and isolation of hard errors (permanent errors) in modern digital circuits are mature, it is very challenging to detect the occurrence of a failure caused by soft-errors in a system. A measure of vulnerability with regard to soft-errors should be available to evaluate circuits that are going to be used in a safety-critical environment. Soft-error sensitivity analysis has since long been used to assess the vulnerability of different parts of a design in the presence of different sources of soft-errors. The process of soft-error analysis is based on stressing the system under test with soft-errors.

Fault-injection has been used for many years as a method of soft-error analysis [Dav09]. Fault-injection works by injection of a predefined model of soft-errors in different parts of a design, for different applications. The fault-injection further determines the functional response of a circuit with regard to the injected soft-errors. Fault-injection is generally a very time-consuming and complex procedure since it requires to inject soft-errors in different logic states of a system (or at least the majority of states).

Fault-injection provides several advantages [Zia04]. To name a few, one can mention that the designer is able to understand the effects of soft-errors in a system under test. Moreover, if a protection mechanism is used in a system, fault-injection can be used to assess the efficiency of those mechanisms. Fault-injection can also be used to discover faulty behaviour of a system which is hidden during the normal tests. Finally, fault-injection needs to be carried out if a processor system is in operation. So it can be used to explore the behaviour of different benchmarks with regard to soft-errors.

Fault-injection can be carried out at different levels of abstraction. In general, there are four categories of fault-injection, including Hardware-Based Fault-injection, Software-Based Fault-injection, Simulation-Based Fault-injection and Emulation-based Fault-injection. The following paragraphs will briefly explain the different categories. The main focus is to list the benefits and drawbacks of each method [Zia4, Zha07, Dav09].

#### 2.4.1 Hardware-based fault-injection techniques

Hardware-Based Fault-Injection (HBFI) techniques are conducted by stressing the actual hardware with real environmental sources which are responsible for soft-errors. Those environmental parameters can be laser-based radiation [Pou00], power-supply disturbance [Hut09], and Electro-Migration Interference (EMI) [Var05]. HBFI techniques can be further categorized into [Zia04]:

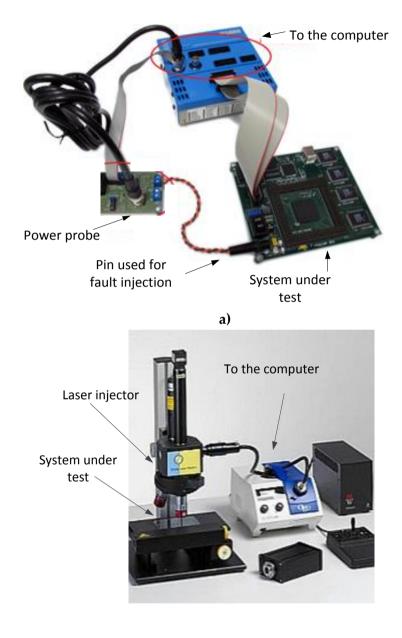

HBFI techniques with contacts; in this category the fault injector is in <u>direct</u> physical contact with the system under test. The injector produces voltage or current changes externally to the target chip. Figure 2.5a shows a power-supply injector which is being used for fault-injection at the chip pins. This power supply (blue box) generates a disturbance and this disturbance will be consequently injected in the chip by a power probe.

In the case of HBFI without contact the injector has <u>no direct</u> physical contact with the system under test; an external source produces some physical activity, such as heavy-ion radiation to evoke a predefined disturbance of soft-errors in the circuit. Figure 2.5b shows a laser-based fault-injection which injects a very accurate laser beam into a system. The laser beam is used to modify the contents of a chip, while the white box provides the proper characteristics of the laser that is being injected to the chip. This method of fault-injection needs to be highly accurate in positioning especially with the current trend of shrinking chip technology dimensions.

b)

Figure 2.5. a) Fault-injection at chip pins. b) Laser-based fault-injection (both pictures are a courtesy of [Opt12]).

Even though conducting hardware-based fault-injection techniques is very complex and costly, they are very close to the real physical nature of a soft-error. The benefits of hardware-based fault-injection can be summarized as [Zia04]:

The HBFI methods can access locations that cannot be accessed by other fault-injection methods. For example, laser-based fault-injection can inject faults into all the flip-flops (after removing any protective layers) and registers which are simply not accessible by I/O pins or software.

A physical analysis by injection of physical faults into a prototype is sometimes the only practical way to estimate the behaviour of a circuit with regard to soft-errors. This is the case if the source code of the system is not available or there is no simulation model of the predefined soft-error model to conduct fault-injection. Furthermore, there is no need to modify the architecture of the system under test to conduct fault-injection. This is desirable if the system is only available as a prototype.

Meanwhile there are different drawbacks for HBFI methods. Among them is limited observability, which means it is very hard to track an injected fault in the system. Moreover, HBFI techniques require specialpurpose hardware in order to perform the fault-injection experiments.

In this thesis, the results of hardware-based fault-injection from others will be used to develop a simulation model for Single Event Transients (SETs) which can be incorporated in simulation-based fault-injection techniques.

# 2.4.2 Software-based fault-injection techniques

Traditionally, software-based fault-injection techniques modify the software being executed under the operating system. Different sorts of faults can be injected at this level, varying from register and memory faults to faulty network packets. Software fault-injections are more focused on the aspects of a system which are accessible by a software developer, for example the operating system. Software simulations are normally non-intrusive, i.e. the hardware of the system will not be changed. The benefits of

software-based fault-injection techniques are that these techniques can be carried out on the basis of operating systems, which are difficult to conduct using hardware-based fault-injection approaches. Furthermore, experiments can be executed almost in real-time, depending on whether the timing of the system under test is a target of fault-injection or not. This allows running of a large number of fault-injection experiments within a reasonable amount of time. The same amount of time needs to be executed without a fault. Finally, software-based fault-injection techniques do not require any special hardware, and in addition conducting fault-injection experiments by software modification has a low complexity and hence a low development and implementation cost.

However, there are also a number of drawbacks; for example the fault-injection process needs to be executed at assembly language level. Therefore, the flexibility to model different soft-errors are limited. Furthermore, soft-errors cannot be injected into locations that are inaccessible by the software, such as an internal register file. Last but not least, it requires a modification of the source code to carry out fault-injection. As a result, the source code that will be executed for fault-injection will not be the same as the one that will run on the system under normal operational situations.

# 2.4.3 Simulation-based fault-injection techniques

Simulation-based fault-injections [Jen93] involves the construction of a simulation model of the system under analysis, including a detailed simulation model of the circuit which is being used for fault-injection. Moreover, the perturbation should be modelled at the same level as the circuit that has been modelled. The operational failure of the simulated system can occur according to a predetermined distribution of perturbations in order to accelerate the injection of soft-errors. This predetermination helps in terms of a more effective propagation of faults in the system, such as an overlap of an erroneous pulse with the positive clock edge of a flip-flop. First, the simulation model of the system under test is developed using a hardware description language such as VHDL or its American counterpart Verilog. Faults that have been modelled based on VHDL or Verilog are subsequently injected into the VHDL model of the system. The details of

simulation-based fault-injection techniques will be explained in the next chapter. However, as the benefits and drawbacks of this class of faultinjection techniques the following comments can be made:

As a benefit, simulated-based fault-injection techniques can support almost all abstraction levels, from the transistor level up to the architectural level. The only requirement is that a simulation model of the system under test as well as the soft-error should exist at the same hierarchical level. In addition, it is possible to carry out this fault-injection method while the system is still under development. Another advantage is that there is full controllability over when and where a fault is injected into the system. This feature is very important in fault-injection analysis since the hardware-based fault-injection approaches cannot provide this degree of controllability.

Furthermore, the cost of computer infrastructure is low, in terms of special-purpose hardware. It also provides timely feedback to system design engineers because all the results of the simulation can be logged in the simulation computer for further investigation. In addition, during simulation-based fault-injection methods, a fault-injection is performed using the same software that will run in the field.

One of the most beneficiary features of simulation-based faultinjection methods is the degree of observability and controllability. In another words, any signal or register in the design can be accessed and modified. The result of this modification can be traced clock-by-clock in a simulation program.

As drawbacks of simulation-based fault-injection techniques, the following issues can be mentioned:

Fault-injection using simulation-based techniques needs a large development effort as the soft-errors should be modelled at the same hierarchical level as the system under test. Furthermore, conducting this type of fault-injection is very time consuming with regard to the experiment length; this is because carrying out simulation-based fault-injection is employing the simulation of the system in its fault-free version as well as in the presence of possible faults. This fact can cause the experimental length of

these experiments to take several days while the simulation computer needs to run the fault-injection experiments.

#### 2.4.4 Emulation-based fault-injection techniques

In recent years, a new category has been added to the fault-injection methods, known as emulation-based fault-injection techniques. This method injects faults in a circuit description implemented in an FPGA [Civ02, Por07]. This approach combines the efficiency of hardware-based fault-injection techniques and the flexibility of simulation-based fault-injection techniques in one framework. Experimental results have shown that a significant speed-up can be achieved as compared to simulation-based fault-injection techniques. However emulation-based fault-injections are generally only feasible for permanent faults, e.g. stuck-at faults. Moreover, the final circuit should be synthesizable and therefore the usage of test-benches in the fault-injection process is not possible.

The benefits of emulation-based fault-injection techniques are that the injection time is much shorter as compared to simulation-based techniques. This capability allows the designer to have a quick evaluation.

There are also drawbacks of this method, as the initial VHDL description must be synthesizable and optimized to avoid the requirement of a large and costly emulator; in addition a reduction of total running time can be accomplished. This fact limits the usage of test-benches in a circuit. Other disadvantages are that the implementation cost concerns the general hardware emulation system and the implementation of an FPGA-based emulation board. Furthermore, the algorithmic description of a circuit is not yet widely accepted by synthesis tools, and therefore emulation-based fault-injection approaches can often only be applied at the Register-Transfer-Level (RTL) of a system. Finally, it is necessary to have a high-speed communication link between the host computer and the emulation FPGA board which is a critical factor in the emulation set-up.

As a summary of different fault-injection methods, hardware-based methods provide the fastest fault-injection in terms of the required time to carry out experiments; however, conducting such experiments is very costly and complex to control. On the other hand, simulation-based fault-injections provide a high level of controllability to conduct perturbations; however, the required time to conduct such experiments is very long.

# 2.5 Architecture of our target processor

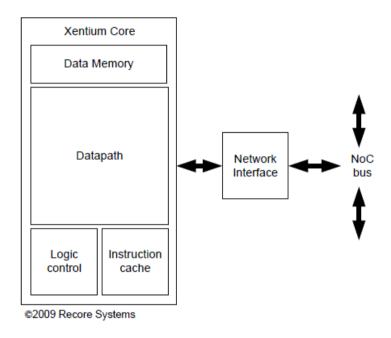

This section provides the baseline architecture of our case study, the Xentium processor®, from Recore Systems [Rec11]. As mentioned before, the goal of this thesis is to investigate the impact of soft-errors on digital processors. This includes the development of a model for soft-errors, assess the impact of soft-errors in a digital processors and also increasing the robustness of digital processors with regard to soft-errors. In order to assess these different criteria we have selected a Digital Signal Processor (DSP), the Xentium processor [Car11, Ker10] from Recore Systems [Rec11]. The Xentium processor is an ultra-low power DSP processor designed for high performance digital signal-based workloads.

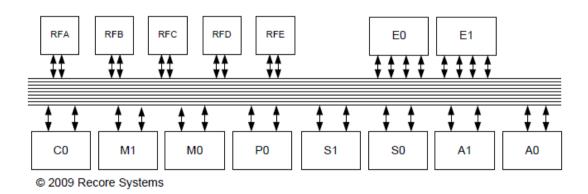

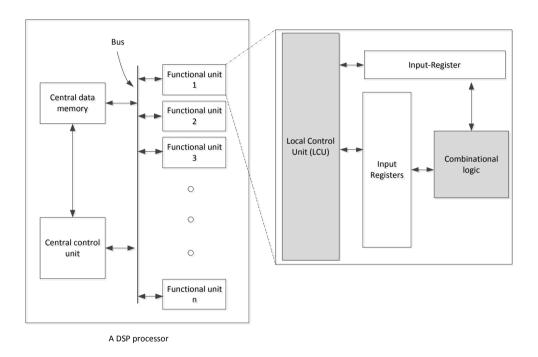

The default architecture of the Xentium core including a data-path, a control unit, an instruction cache, a network interface and memory banks is shown in Figure 2.6. The memory banks are static RAMs that are communicating with the data-path in parallel to increase parallelism. A detailed architecture of the data-path is shown in Figure 2.7. The data-path has been designed based on a Very Large Instruction Word (VLIW) architecture that consists of ten functional units and five register files. Each functional unit is responsible for a certain class of instructions. For example, E units (E0 and E1) perform load/store instructions, M units (M0 and M1) are multipliers that are useful for accumulation operations. P and C units (P0 and C0) are used in those operations where the Program Counter (PC) is involved. Finally A (A0 and A1) and S units (S0 and S1) perform arithmetic and logical operations. All functional units can access five register files (RFA, RFB, RFC, RFD and RFE) in parallel. An actual implementation of the Xentium processor is based on 90nm CMOS technology leading to a silicon area of 1.2mm<sup>2</sup> and running on a clock frequency of 200MHz.

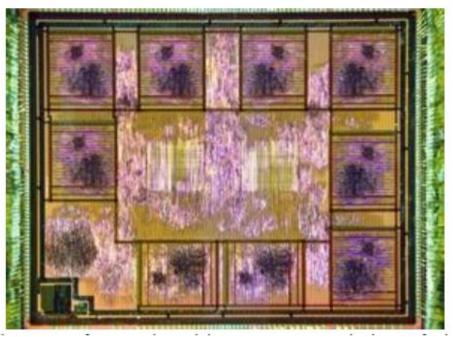

This processor has been developed as part of a multi-core System-on-Chip (SoC) system as depicted in Figure 2.8. This chip contains nine Xentium cores, interconnected by a NoC. Each of the single cores are able to connect to the adjacent routers, while the routers are connected to a Network-on-Chip (NoC). The NoC can be connected to more conventional bus architectures to communicate with other peripherals, if required.

Different parts of the Xentium processor will be elaborated in different chapters of this thesis. More details of each part of the processor will be discussed in the most appropriate chapter concerned.

Figure 2.6. Xentium processor with memory and network interface [Rec11].

Figure 2.7. The Xentium data-path architecture [Rec11].

Figure 2.8 Photomicrograph of the multicore SoC consisting of nine Xentium core processors [Rec11].

#### 2.6 Conclusions

This chapter provides the basic background with regard to soft-errors. The sources of soft-errors were discussed and also the terminology of soft-errors was provided. Different evaluation methods with regard to the effect of soft-errors in a digital system, including hardware, software, emulation and simulation-based fault-injections were covered in this chapter. Furthermore, the basic architecture of our case study has been introduced, the Xentium processor. The Xentium processor will be used later on in the evaluation of our proposed fault-injection method; also its architecture will be modified to develop a reliable DSP architecture to mitigate the effect of soft-errors.

## References

- [Adv05] S. Adve, P. Sanda, "Reliability aware microarchitecture," in the IEEE/ACM International Symposium on Microarchitecture, Vol. 25, No. 6, pp. 8–9, 2005.

- [Anc03] L. Anchordoqui, T. Paul, S. Reucroft et al. "Ultra-high energy cosmic rays: The state of the art before the auger observatory," in International Journal of Modern Physics, Vol. 18, pp. 2229–2366, 2003.

- [Bau02] R. Baumann, "Soft-errors in Commercial Semiconductor Technology: Overview and Scaling Trends," in IEEE Reliability Physics Tutorial Notes, Reliability Fundamentals, pp. 1–14, 2002.

- [Bau05] R. Baumann, "Radiation-induced soft-errors in advanced semiconductor technologies," in IEEE Transactions on Device and Materials Reliability, Vol. 5, No. 3, pp. 305–316, 2005.

- [Car11] J. Cardoso, M. Hubner, "Reconfigurable computing, from FPGAs to hardware/software co-design," Springer, ISBN 978-1-4614-0061-5, 2011.

- [Cis03] Cisco 12000 Single Event Upset Failures Overview and Work Around Summary, <a href="http://www.cisco.com/en/US/ts/fn/200/fn25994.html">http://www.cisco.com/en/US/ts/fn/200/fn25994.html</a>, 2003.

- [Civ02] P. Civera, M. Macchiarula, "An FPGA-Based approach for speeding-up fault-injection campaigns on safety-critical circuit," in Journal of Electronic Testing: theory and applications (JETTA), Vol. 18, No. 3, pp. 261-271, 2002.

- [Cro99] A. Crouch, "Design-for-test for digital IC's and embedded core systems," Prentice Hall, ISBN 978-0130848277, 1999.

- [Dav09] J. M. Daveau, A. Blampey, G. Gasiot et al., "An industrial fault-injection platform for soft-error dependability analysis and hardening of complex system-on-a-chip," in the Proceedings of IEEE International Reliability Physics Symposium (IRPS), pp. 212-220, 2009.

- [Dir03] J. D. Dirk, M. E. Nelson, J. F. Ziegler, et al., "Terrestrial thermal neutrons," in IEEE Transactions on Nuclear Science, Vol. 50, No. 6, pp. 2060–2064, 2003.

- [For00] D. Lyons, "Sun Screen," in Forbes Magazine, http://members.forbes.com/global/2000/1113/0323026a.html, 2000.

- [Hut09] M. Hutter, J. M. Schmidt, T. Plos, "Contact-Based fault-injections and power analysis on RFID tags," in European Conference on Circuit Theory and Design, pp. 409-412, 2009.

- [Jen93] E. Jenn, M. Rimen, J. Ohlsson et al., "Design guidelines of a VHDL-Based simulation tool for the validation of fault tolerance," in Proceedings of Open Workshop LAAS/CNRS, pp. 461-483, 1993.

- [Ker10] H. G. Kerkhoff, X. Zhang, "Design of an infrastructural IP dependability manager for a dependable reconfigurable many-core processor," in IEEE

- International Symposium on Electronic Design, Test and Applications (DELTA), pp. 270-275, 2010.

- [Nic11] M. Nicolaidis, "Soft-errors in modern electronic systems," Springer, ISBN 978-1-4419-6993-4, 2011.

- [Ols93] J. Olsen, P. E. Becher, P. B. Fynbo, et al., "Neutron induced Single Event Upsets (SEUs) in Static RAMs observed at 10km flight altitude," in IEEE Transactions on Nuclear Science, Vol. 40, pp. 120-126, 1993.

- [Opt12] www.opto.de, 2012.

- [Pou00] V. Pouget, D. Lewis, P. Fouillat, "Time-resolved scanning of integrated circuits with a pulsed laser: application to transient fault-injection in an ADC," in IEEE Transactions on Instrumentation and Measurement, Vol. 53, No. 4, pp. 1227-1231, 2000.

- [Pou07] M. Portela-Garcia, L. O. Celia, M. Garcia-Valderas et al., "A rapid fault-injection approach for measuring SEU sensitivity in complex processors," in IEEE International On-Line Testing Symposium, pp. 101-106, 2007.

- [Rec11] Recore-systems, http://www.recoresystems.com/, 2011.

- [Sha11] S. Z. Shazli, "High level modeling and mitigation of transient errors in nanoscale systems," PhD Thesis, ISBN 3443832, Northeastern University, 2011.

- [Shi02] P. Shivakumar, M. Kistler, S. W. Keckler, et al., "Modelling the effect of technology trends on the soft-error rate of combinational logic," in the Proceedings of International Conference on Dependable Systems and Networks (DSN), pp. 1-10, 2002.

- [Tab93] A. Taber and E. Normand, "Single Event Upset in avionics," in IEEE Transactions on Nuclear Science, Vol. 40, pp. 120-126,1993.

- [Var05] F. Vargas, D. L. Cavalcante, E. Gatti, et al., "On the proposition of an EMI-Based fault-injection approach," in IEEE International On-Line Testing Symposium (IOLTS), pp. 207-208, 2005.

- [Wan07] N. J. Wang, "Cost effective soft-error mitigation in microcontrollers," PhD Thesis, ISBN 978-1-4114-8598-5, University of Illinois at Urbana-Champaign, 2007.

- [Yuh11] H. Yu, "Low-cost highly-efficient fault tolerant processor design for mitigating the reliability issues in nano-metric technologies," PhD Thesis, ISBN 978-1-1275-3245-1, TIMA Lab., 2011.

- [Zha07] W. Zhang, X. Fu, T. Li, et al., "An analysis of microarchitecture vulnerability to soft-errors on simultaneous multithreaded architectures," in IEEE International Symposium on Performance Analysis of Systems and Software (PASS), pp. 169-178, 2007.

- [Zia04] H. Ziade, R. Ayoubi and R. Velazco, "A survey on fault-injection techniques," in the International Arab Journal of Information Technology, Vol. 1, pp. 171-186, 2004.

- [Zie81] J. F. Ziegler and W. A. Lanford, "The effect of sea level cosmic rays on electronic devices," in the Journal of Applied Physics, Vol. 52, pp. 4305–4312, 1981.

- [Zie96] J. F. Ziegler, H. W. Curtis, H. P. Muhlfeld et al., "IBM experiments in soft fails in computer electronics," in IBM Journal, Vol. 40, pp. 3-18, 1994.

# CHAPTER 3

A Framework for Accelerating Soft-Error Analysis in HDL Designs

Parts of this chapter have been published in the papers titled "A technique for accelerating injection of transient faults in complex SoCs" in the IEEE Euro-micro conference on digital system design in 2011, "Study of the effects of SET induced faults on sub-micron technologies" in the IEEE/IFIP international conference on dependable systems and networks in 2011 and "Rapid transient fault insertion in large digital systems" in the Elsevier journal of microprocessors and microsystems in 2013.

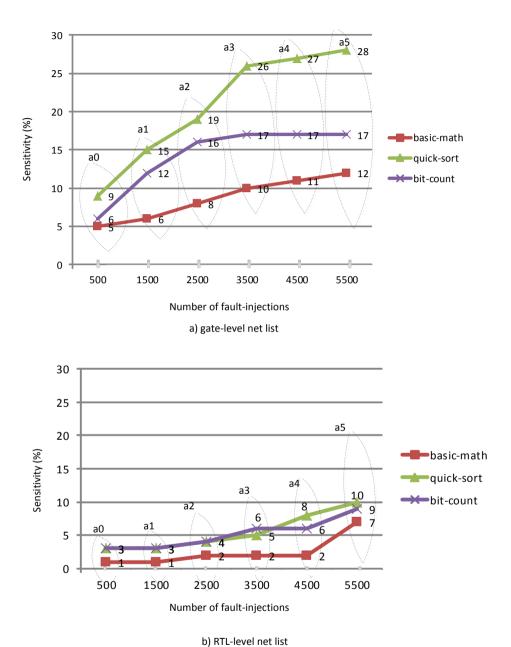

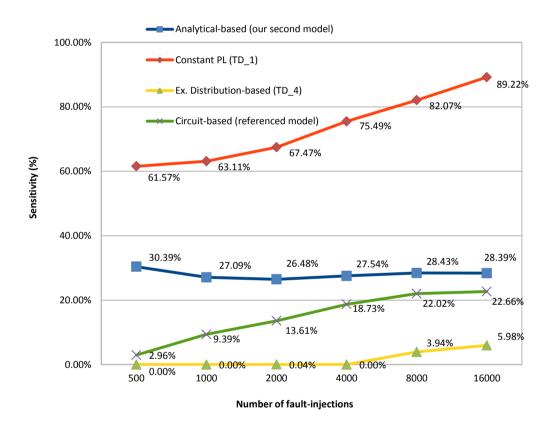

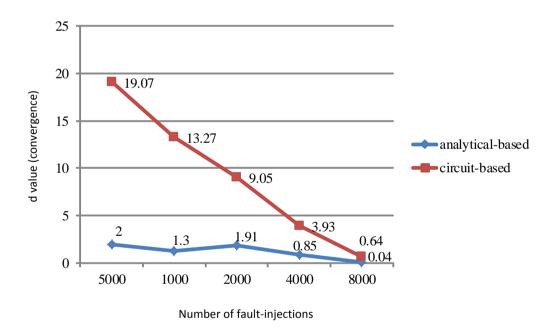

ABSTRACT - This chapter introduces two contributions in terms of simulation-based fault-injection in HDL designs. The first contribution concerns acceleration of soft-error injection in HDL designs, with regard to the elapsed CPU time, which is the real time to conduct fault-injections. The second contribution is dealing with conventional challenges in conducting simulation-based fault-injection, i.e. the importance of timing information in the net list on the accuracy of fault-injection results, as well as reaching the point of convergence in fault-injection results. The latter observation assures the designer that fault-injection results are not dependent on the number of fault-injections any longer. The introduced fault-injection framework is capable of simulating various fault models in a comparable elapsed CPU time, as compared to other conventional simulation-based fault-injections on a DSP processor and comparing the elapsed CPU time to some conventional fault-injection tools. These experiments showed that the developed framework is capable of reducing the elapsed CPU time by a factor ranging from 27% to 67% as compared to conventional simulation-based fault-injection tools, and by a factor of 10% compared to available accelerated simulation-based frameworks.

#### 3.1 Introduction

This chapter introduces a simulation framework to conduct simulation-based soft-error studies, as the first approach to deal with soft-errors.

As discussed in Chapter 2, simulation-based fault-injections are being used as a very detailed and accurate experimental method to assess the sensitivity of a system with regard to soft-errors, in the academic community as well as in the industrial world [Pec13]. Simulation-based fault-injection uses a simulation model of the system to evoke predefined fault models into different parts of a system. The simulation model of the system can be developed using any hardware description language, such as VHDL, Verilog or SystemC. The predefined fault models can also be described in any hardware language due to the availability of several integrated simulators which are able to simulate a design which is consisting of several types of HDL languages.

Simulation-based fault-injections provide various advantages which make them very popular for soft-error analysis [Bar05]. Issues are a high controllability over where and when a fault should be evoked, as well as a high observability in terms of the propagation of faults. Very important is the fact that the designer is able to conduct soft-error analysis even before the system is actually implemented. However, there are a number of

downsides regarding some facets of simulation-based fault-injections. The first concern is that simulation-based fault-injections require an extensive period of Central-Processing-Unit (CPU) time of the host computer to conduct fault-injection experiments, or elapsed CPU time. This phenomenon is known as the CPU intensiveness [Zia04]. A long elapsed CPU time is induced by the fact that the simulation time is several orders of magnitude longer compared to the real time. Hence a comprehensive simulation-based fault-injection might take several days to be accomplished.

The second concern is due to the fact that the accuracy of fault-injection results strongly depends on the level of hierarchy in which simulation-based fault-injections are conducted [Nic11]. This means the results of fault-injections will lead to different results if fault-injection experiments are carried out on a front-end HDL model (Register Transfer Level, RTL) versus a back-end HDL model (such as post-synthesized logic gate-level net list, including timing information). This issue will become more important as a number of emerging soft-error standards, such as the Reliability Information Interchange Format, RIIF [Ava12], focus on the RTL hierarchy level; this provides a universal soft-error library regardless of the final library in which a circuit will be implemented. The results of this chapter will show that fault-injection results can be interpreted differently if the timing information in a net list (which is represented at the logic gate-level net list) is disregarded.

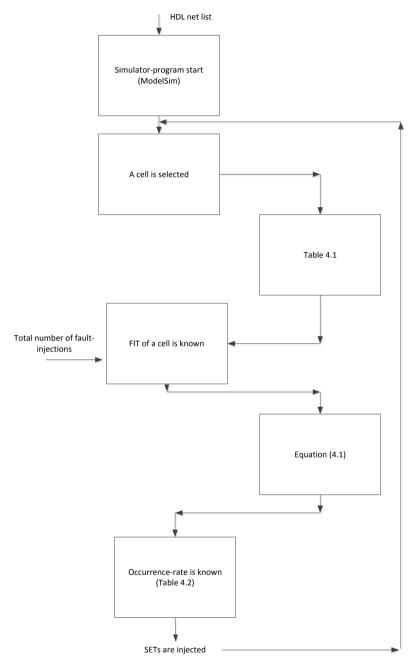

In this chapter, the CPU intensiveness of simulation-based fault-injections is addressed by developing a framework to speed-up injection of conventional models of soft-errors in a HDL design. Simulation-based fault analysis is composed of three different phases, set-up, fault-injection and evaluation phases. Our developed framework accelerates the whole simulation-based fault analysis by speeding up the fault-injection phase, while the set-up and evaluation phases are identical to other conventional fault-injection methods. It is also important to mention that the framework in this chapter has been developed to inject conventional models of soft-errors, i.e. the bit-flip model for Single-Event-Upsets (SEUs) and the momentary rectangular pulse for Single-Event-Transients (SETs) [Kar04], as discussed in Chapter 2.

Another subject of this chapter is the contribution on the level of granularity of the system under analysis in producing an accurate fault-injection. This issue will be addressed by conducting identical simulation-based fault analysis on a Digital Signal Processing (DSP) processor at two levels of hierarchies, a <u>post</u> placed-and-routed gate-level net list (including timing information), and a <u>pre</u>-placed-and-routed RTL net list. It will be shown that taking the timing information in a net list into account contributes to a faster convergence of fault-injection results. The latter issue is very important since reaching a point of convergence in simulation-based fault analysis is a metric which indicates that the fault-injection results are no longer dependent on the number of simulations.

The framework which will be presented in this chapter, will serve as a preliminary step in conducting soft-error evaluation studies. The outcome of this framework helps to distinguish the sensitivity of gates/nets of a system, with regard to soft-errors. Consequently, these sensitive parts will be enhanced with soft-error mitigation methods to decrease the level of soft-error vulnerability.

The remainder of this chapter is organized as follows: section 3.2 discusses state-of-the-art simulation-based fault analysis as well as the accelerated ones. Section 3.3 discusses the details of the developed framework. The achievements in terms of CPU intensiveness will be presented in Section 3.4 while the importance of hierarchical levels will be treated in Section 3.5. Finally, Section 3.6 will conclude this chapter.

# 3.2 Simulation-based fault analysis

The first step to conduct a simulation-based fault analysis is to represent the circuit under analysis in one of the HDL languages (VHDL, Verilog or SystemC). The next step involves perturbation of registers or nets according to a predetermined perturbation model, referred to as the fault model. This latter step is known as the fault-injection phase. An elementary simulation-based fault-injection experiment corresponds to one simulation execution during which one predefined fault model is injected into the simulation environment [Zia04]. A series of such simulations constitutes a simulation-based fault-injection campaign. A simulation-based fault-

injection campaign might be composed of thousands of simulation-based fault-injection experiments. Finally, the logged results of the fault-injection campaign need to be interpreted to establish the sensitivity of the circuit under analysis or parts of it with regard to the injected fault model. This last step is formally known as the evaluation phase.

In order to discuss the development of our framework, first the stateof-the-art techniques that have been used in the fault-injection phase will be briefly presented. Then, the integration of two different approaches into one platform will be discussed in order to use their benefits in accomplishing an accelerated simulation-based fault-injection.

#### 3.2.1 State-of-the-art simulation-based fault-injection

In general, implementing the fault-injection phase of a simulation-based fault analysis can be divided into two categories [Bar04, Zia04, Gra10]:

- using built-in commands of the simulator program, which approach is known as "built-in commands".

- using code-modifications techniques, which can be further divided into saboteur and mutant methods.

#### 3.2.1.1 Built-in commands

Built-in commands are based on using, at simulation time, built-in commands of the HDL simulator in order to modify the value/timing of a net or register. This approach normally provides the fastest performance with regard to the total elapsed CPU time, since it does not modify any part of the representation of the circuit under analysis. However, the applicability of this technique strongly depends on the functionality of the built-in commands of the simulator program [Lee09]. For example, whether a momentary change in a value of a net is feasible or not depends on whether the force command has been embedded in a simulator kernel or not.

One of the most widely-used techniques in the built-in commands category is to disconnect a particular signal (target signal for fault-injection) from its input(s) at a certain point of time (so-called 'time instance'); then force it to a new value for a brief period of time (so-called 'fault duration').

For example, to inject a temporary pulse on a signal named 'V' at a time-instant 'T<sub>1</sub>', the sequence of the following pseudo-commands should be executed [Gaw10] as shown in Figure 3.1.:

1- simulate-until @ (T1) ns

2- force-signal (V) to (faulty-value)

3- simulate until @ ('fault duration') ns

4- release-signal (V)

5- simulation-continue

6- result-logged

Figure 3.1. Pseudo-commands of built-in simulation fault-injection.

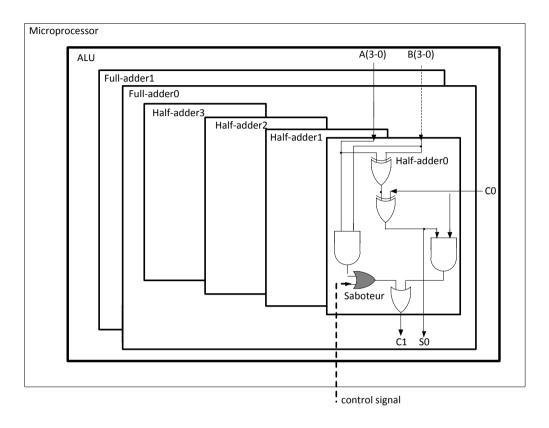

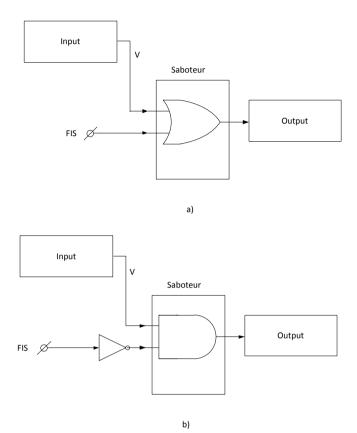

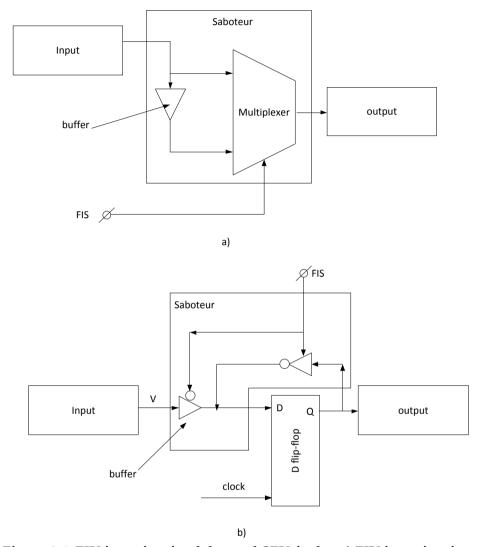

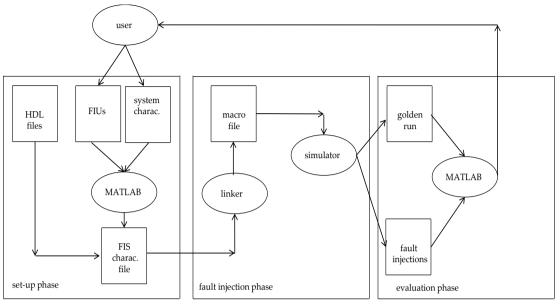

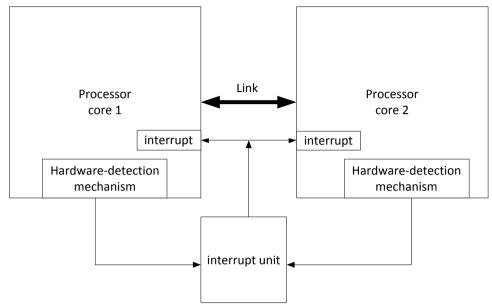

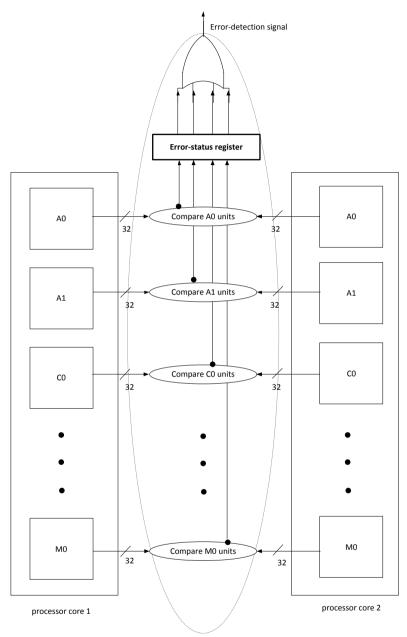

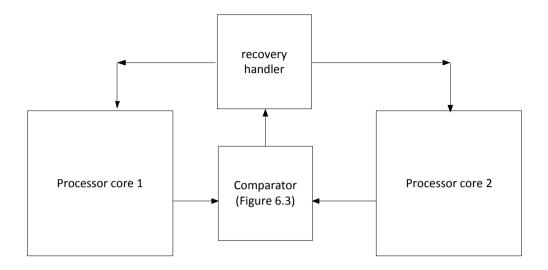

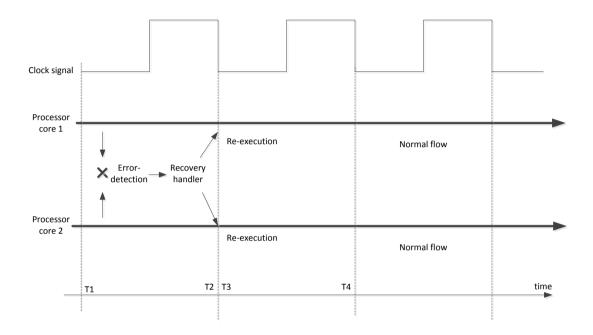

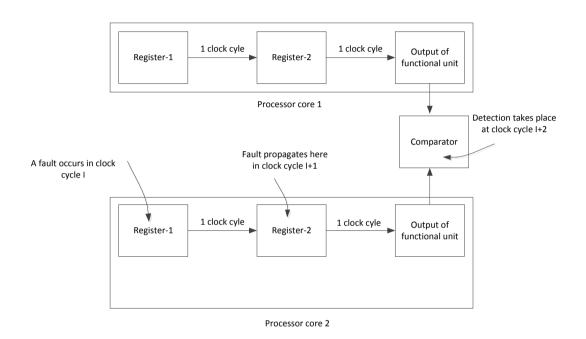

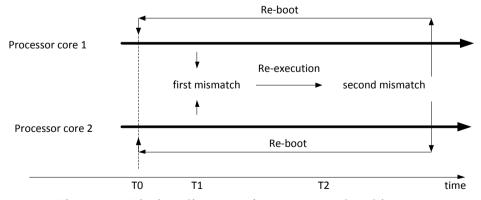

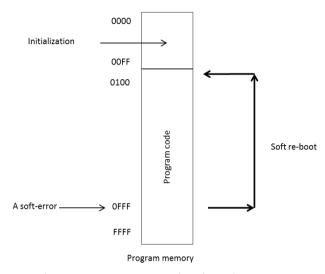

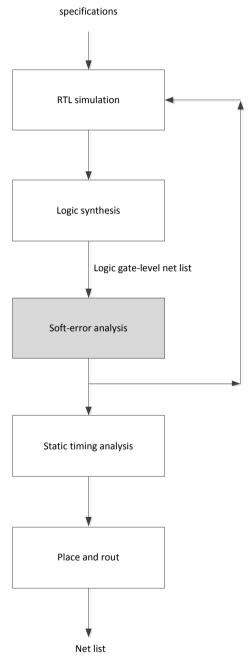

Several existing frameworks exploit the built-in commands for the fault-injection phase. MEFISTO [Jen94] was one of the first tools that employed built-in commands in the fault-injection phase. Another example is GSTF [Bar00] which is a VHDL-based fault-injection tool, was built based on the built-in commands of a commercial VHDL simulator (V-System®). It is capable of injecting soft-errors into different levels of hierarchy, which can be logic gate-, RTL- and chip-level.